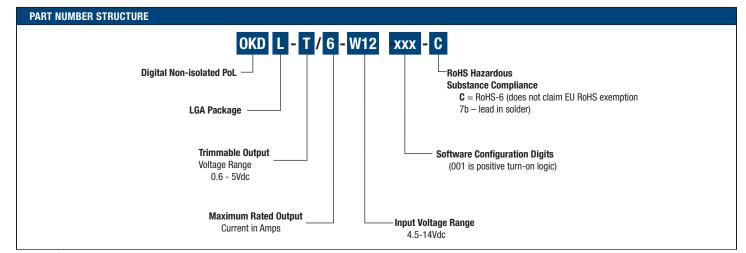

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

#### **FEATURES**

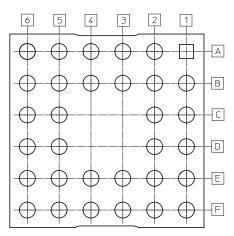

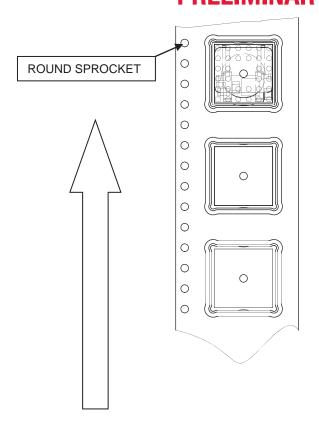

■ Small package: 12.2 x 12.2 x 8.0 mm (0.48 x 0.48 x 0.315 in)

Typical unit

- 0.6 V 5 V output voltage range

- High efficiency, typ. 91.6% at 12Vin, 5Vout and 50% load

- Configuration Control and Monitoring via PMBus

- Adaptive compensation of PWM control loop & fast loop transient response

- Synchonization input & phase spreading/interleaving

- Voltage Tracking & Voltage margining

- MTBF 24 Mh

- For narrow board pitch applications (15 mm/0.6 in)

- Pre-bias start-up & shut down

- Monotonic & Soft start Power up

- Input under voltage shutdown; OTP, output OVP, OCP

- Remote control & Power Good

- Differential sense pins

- Voltage setting via pin-strap or PMBus

- Advanced Configurable via Graphical User Interface

- ISO 9001/14001 certified supplier

- Highly automated manufacturing ensures quality

#### **PRODUCT OVERVIEW**

TRD

### **Applications**

- Distributed power architectures

- Intermediate bus voltage applications

- Servers and storage applications

- Network equipment

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

| ORDERING GUIDE     |                      |  |  |  |

|--------------------|----------------------|--|--|--|

| Model Number       | Output               |  |  |  |

| OKDL-T/6-W12-001-C | 0.6-5.0 V, 6 A/ 30 W |  |  |  |

#### **Absolute Maximum Ratings**

| Character                                 | Characteristics                                                                             |                                            |      | Тур | Max | Unit |

|-------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------|------|-----|-----|------|

| T <sub>P1</sub>                           | Operating tempe                                                                             | rature (see Thermal Consideration section) | -40  |     | 120 | °C   |

| Ts                                        | Ts Storage temperature                                                                      |                                            |      |     | 125 | °C   |

| Vı                                        | Vi Input voltage (See Operating Information Section for input and output voltage relations) |                                            | -0.3 |     | 18  | V    |

| Logic I/O v                               | Logic I/O voltage CTRL, SAO, SA1, SALERT, SCL, SDA, VSET, SYNC, PG, CS_VTRK                 |                                            | -0.3 |     | 4   | V    |

| Ground voltage differential -S, PREF, GND |                                                                                             | -0.3                                       |      | 0.3 | V   |      |

| Analog pin                                | voltage                                                                                     | V0, +S                                     | -0.3 |     | 5.5 | V    |

| General and Safety | Conditions                         | Min | Тур  | Max | Unit |

|--------------------|------------------------------------|-----|------|-----|------|

| Safety             | Designed for UL/IEC/EN 60950 1     |     |      |     |      |

| Calculated MTBF    | Telcordia SR-332, Issue 2 Method 1 |     | 14.2 |     | Mhrs |

Stress in excess of Absolute Maximum Ratings may cause permanent damage. Absolute Maximum Ratings, sometimes referred to as no destruction limits, are normally tested with one parameter at a time exceeding the limits in the Electrical Specification. If exposed to stress above these limits, function and performance may degrade in an unspecified manner.

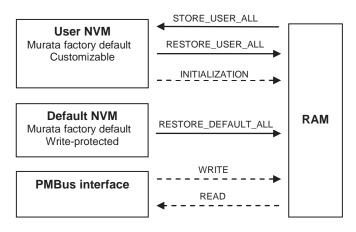

#### **Configuration File**

This product is designed with a digital control circuit. The control circuit uses a configuration file which determines the functionality and performance of the product. The Electrical Specification table shows parameter values of functionality and performance with the default configuration file, unless otherwise specified. The default configuration file is designed to fit most application needs with focus on high efficiency. If different characteristics are required it is possible to change the configuration file to optimize certain performance characteristics.

In this Technical specification examples are included to show the possibilities with digital control. See Operating Information section for information about trade offs when optimizing certain key performance characteristics.

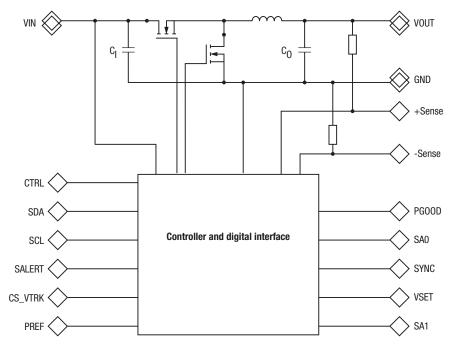

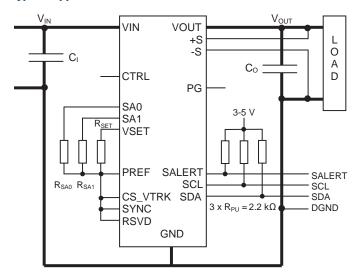

**Fundamental Circuit Diagram**

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

#### **Electrical Specifications**

$T_{P1} = -30 \text{ to } +95 ^{\circ}\text{C}, \, VI = 4.5 \text{ to } 14 \text{ V}, \, VI > VO + 1.0 \text{ V}$

Typical values given at:  $T_{P1} = +25^{\circ}C$ ,  $V_1 = 12.0$  V, max  $I_0$ , unless otherwise specified under Conditions.

Default configuration file, 190 10-CDA 102 0518/001.  $V_0$  defined by pin strap.

External  $C_{IN}=47~\mu F$  ceramic + 270  $\mu F/10~m\Omega$  electrolytic,  $C_{OUT}=3x100~\mu F+0.1~\mu F$  ceramic.

See Operating Information section for selection of capacitor types. Sense pins are connected to the output pins.

| Charac           | cteristics                                 |                               | Conditions                                                                                                                               | Min  | Тур   | Max  | Unit             |

|------------------|--------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------------------|

| V,               | Input voltage                              |                               |                                                                                                                                          | 4.5  |       | 14   | V                |

|                  | Output voltage without                     | pin strap                     |                                                                                                                                          |      | 0     |      | V                |

|                  | Output voltage adjustme                    |                               |                                                                                                                                          | 0.60 |       | 5.0  | V                |

|                  | Output voltage adjustme                    | ent including PMBus margining |                                                                                                                                          | 0.50 |       | 5.25 | V                |

|                  | Output voltage set-poin                    |                               |                                                                                                                                          |      | 1.2   |      | mV               |

|                  | Output voltage accuracy                    |                               | Including line, load, temp                                                                                                               | -1   |       | 1    | % V <sub>0</sub> |

|                  | Internal resistance +S/-                   |                               |                                                                                                                                          |      | 47    |      | Ω                |

|                  | +S bias current                            |                               |                                                                                                                                          |      | 50    |      | μА               |

|                  | -S bias current                            |                               |                                                                                                                                          |      | -35   |      | μA               |

| .,               |                                            |                               | $V_0 = 0.6 \text{ V}$                                                                                                                    |      | 1     |      | ·                |

| $V_0$            |                                            |                               | $V_0 = 1.2 \text{ V}$                                                                                                                    |      | 2     |      | 1                |

|                  | Line regulation                            | $I_0 = \max I_0$              | $V_0 = 1.8 \text{ V}$                                                                                                                    |      | 3     |      | mV               |

|                  |                                            |                               | $V_0 = 3.3 \text{ V}$                                                                                                                    |      | 4     |      | 1                |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 7     |      | 1                |

|                  |                                            |                               | $V_0 = 0.6 \text{ V}$                                                                                                                    |      | 1     |      |                  |

|                  |                                            |                               | $V_0 = 1.2 \text{ V}$                                                                                                                    |      | 1     |      | 1                |

|                  | Load regulation                            | $I_0 = 0 - 100\%$             | $V_0 = 1.8 \text{ V}$                                                                                                                    |      | 1     |      | mV               |

|                  |                                            |                               | $V_0 = 3.3 \text{ V}$                                                                                                                    |      | 2     |      | 1                |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 2     |      | ]                |

|                  |                                            |                               | $V_0 = 0.6 \text{ V}$                                                                                                                    |      | 10    |      |                  |

|                  | Output ripple & noise                      |                               | $V_0 = 1.2 \text{ V}$                                                                                                                    |      | 10    |      | ]                |

| V <sub>oac</sub> |                                            |                               | $V_0 = 1.8 \text{ V}$                                                                                                                    |      | 11    |      | mVp-p            |

|                  | (up to 20 MHz)                             |                               | $V_0 = 3.3 \text{ V}$                                                                                                                    |      | 19    |      |                  |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 25    |      |                  |

| I <sub>0</sub>   | Output current                             |                               |                                                                                                                                          | 0    |       | 6    | Α                |

| 10               | Output current                             |                               | V <sub>0</sub> = 0.6 V                                                                                                                   | 0    | 0.38  | 0    |                  |

| I <sub>s</sub>   |                                            |                               | $V_0 = 1.2 \text{ V}$                                                                                                                    |      | 0.70  |      | 1                |

|                  | Static input current at max I <sub>0</sub> |                               | $V_0 = 1.8 \text{ V}$                                                                                                                    |      | 1.00  |      | A                |

| 'S               | otatio input current at n                  | 14X 10                        | $V_0 = 3.3 \text{ V}$                                                                                                                    |      | 1.75  |      | ^                |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 2.63  |      | -                |

| I <sub>lim</sub> | Current limit threshold                    |                               | V <sub>0</sub> = 0.0 V                                                                                                                   |      | 9     | 11   | Α                |

|                  |                                            |                               | RMS, hiccup mode,                                                                                                                        |      |       |      |                  |

| I <sub>sc</sub>  | Short circuit current                      |                               | $V_0 = 3.3 \text{ V}, 4 \text{ m}\Omega \text{ short}$                                                                                   |      | 3     |      | A                |

|                  |                                            |                               | $V_0 = 0.6 \text{ V}$                                                                                                                    |      | 70.1  |      |                  |

|                  |                                            |                               | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.2 \text{ V}$                                                                                           |      | 81.8  |      | 1                |

|                  |                                            | EOV of mov l                  | $V_0 = 1.2 \text{ V}$<br>$V_0 = 1.8 \text{ V}$                                                                                           |      | 86.4  |      | - %              |

|                  |                                            | 50% of max I <sub>0</sub>     | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$                                                                                           |      | 91.0  |      | 70               |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 93.3  |      | 1                |

| η                | Efficiency                                 |                               | $V_0 = 0.6 \text{ V}$                                                                                                                    |      | 78.5  |      |                  |

|                  |                                            |                               | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.2 \text{ V}$                                                                                           |      | 87.3  |      | 1                |

|                  |                                            | I - may I                     | $V_0 = 1.2 \text{ V}$<br>$V_0 = 1.8 \text{ V}$                                                                                           |      | 90.7  |      | - %              |

|                  |                                            | $I_0 = \max I_0$              | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$                                                                                           |      | 94.0  |      | - 70             |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 95.6  |      | 1                |

|                  |                                            | 1                             | $V_0 = 5.0 \text{ V}$<br>$V_0 = 0.6 \text{ V}$                                                                                           |      | 0.99  |      | -                |

|                  |                                            |                               | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.2 \text{ V}$                                                                                           |      | 1.01  |      | 1                |

|                  | Power dissipation at ma                    | av I                          | $V_0 = 1.2 \text{ V}$<br>$V_0 = 1.8 \text{ V}$                                                                                           |      | 1.12  |      | W                |

| d                | ower dissipation at Illa                   | 10                            | $V_0 = 1.8 \text{ V}$<br>$V_0 = 3.3 \text{ V}$                                                                                           |      | 1.12  |      | - vv             |

|                  |                                            |                               | $V_0 = 5.0 \text{ V}$                                                                                                                    |      | 1.40  |      | 1                |

|                  |                                            |                               | $V_0 = 0.6 \text{ V}$                                                                                                                    |      | 0.70  |      | +                |

| 1                |                                            |                               | $V_0 = 0.0 \text{ V}$<br>$V_0 = 1.2 \text{ V}$                                                                                           |      | 0.70  |      | 1                |

|                  | Input idling power                         |                               | v 0 - 1.2 v                                                                                                                              |      |       |      | -l               |

| P                | Input idling nower                         | $I_0 = 0$                     | $V_0 = 1.8 \text{ V}$                                                                                                                    |      | () 71 |      | W                |

| P <sub>ii</sub>  | Input idling power                         | $I_0 = 0$                     | $V_0 = 1.8 \text{ V}$                                                                                                                    |      | 0.71  |      | W                |

| P <sub>li</sub>  | Input idling power                         | $I_0 = 0$                     | $V_0 = 3.3 \text{ V}$                                                                                                                    |      | 0.80  |      | W<br>-           |

| P <sub>ii</sub>  | Input idling power                         | $I_0 = 0$                     | $\begin{aligned} &V_0 = 1.8 \text{ V} \\ &V_0 = 3.3 \text{ V} \\ &V_0 = 5.0 \text{ V} \\ &\text{Turned off with CTRL-pin} \end{aligned}$ |      |       |      | w<br>W           |

6A Digital PoL DC-DC Converter Series

## **PRELIMINARY**

| Characte                         | eristics                                       |                              | Conditions                                        | Min                                                                     | Тур                                          | Max      | Unit             |

|----------------------------------|------------------------------------------------|------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------|----------|------------------|

|                                  | Internal output capaci                         | tance                        | $V_0 = 0 \text{ V}$                               |                                                                         | 47                                           |          |                  |

| $C_0$                            | omai output oapaoi                             | V                            | $V_0 = 3.3 \text{ V}$                             |                                                                         | 24<br>15                                     |          | μF               |

|                                  |                                                |                              | $V_0 = 5.0 \text{ V}$<br>Effective capacitance    |                                                                         | 15                                           |          |                  |

| C <sub>OUT</sub>                 | Total output capacitan                         | ce                           | Note 1                                            | 55                                                                      |                                              |          | μF               |

|                                  |                                                |                              | Load step 25-75-25% of max I <sub>0</sub> , di/dt |                                                                         |                                              |          |                  |

| V <sub>tr1</sub>                 | Load transient peak vo                         | oltage deviation             | = 1.5 A/µs                                        |                                                                         | 50                                           |          | mV               |

| t <sub>tr1</sub>                 | Load transient recover                         | ry time                      | $C_0$ =3x100 µF + 270 µF $V_0$ = 3.3 V            |                                                                         | 13                                           |          | μs               |

|                                  | Switching frequency                            |                              |                                                   |                                                                         | 600                                          |          | kHz              |

| F <sub>sw</sub>                  | Switching frequency r                          | ange                         | PMBus configurable<br>FREQUENCY_SWITCH<br>Note 2  |                                                                         | 300-1000                                     |          | kHz              |

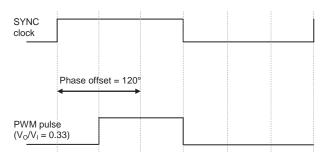

| 311                              | Switching frequency s<br>External Sync Duty Cy |                              |                                                   | -10<br>40                                                               | ±5                                           | 10<br>60 | %<br>%           |

|                                  | Input Clock Frequency                          |                              | External clock source                             | -10                                                                     |                                              | 10       | %                |

|                                  |                                                |                              |                                                   |                                                                         | 4.1                                          |          |                  |

| •                                | ler Voltage Lockout                            | Threshold, V <sub>UVLO</sub> | Rising edge                                       | 3.8                                                                     | 4.1                                          | 4.4      | V<br>            |

| •                                | e controlled)<br>er Voltage Lockout            | Hysteresis                   |                                                   |                                                                         | 0.24                                         |          |                  |

|                                  | e controlled)                                  | Threshold, V <sub>OVLO</sub> | Input rising                                      | 14.3                                                                    | 15.2                                         | 16       | V                |

|                                  | 0 1/ 11                                        | Threshold                    | DMD C 11                                          |                                                                         | 4.35                                         |          | V                |

| input turr                       | n-On Voltage                                   | Threshold range              | PMBus configurable VIN ON                         |                                                                         | 0-14.7                                       |          | V                |

|                                  |                                                | Threshold                    |                                                   |                                                                         | 3.8                                          |          | V                |

| Input Turn-Off Voltage Threshold |                                                | Threshold range              | PMBus configurable<br>VIN OFF                     |                                                                         | 0-14.7                                       |          | V                |

|                                  |                                                | IUVP threshold               |                                                   |                                                                         | 4.1                                          |          | V                |

|                                  |                                                | IUVP threshold range         | PMBus configurable VIN_UV_FAULT_LIMIT             |                                                                         | 0-14.7                                       |          | V                |

|                                  | ler/Over Voltage                               | IOVP threshold               |                                                   |                                                                         | 14.4                                         |          | V                |

| Protection IUVP/ IOV             |                                                | IOVP threshold range         | PMBus configurable<br>VIN_OV_FAULT_LIMIT          |                                                                         | 0-14.7                                       |          | V                |

| ,                                | •                                              | Set point accuracy           |                                                   | -150                                                                    |                                              | 150      | mV               |

|                                  |                                                | Fault response               | VIN_UV_FAULT_RESPONSE                             |                                                                         | ake continuous rest                          |          |                  |

|                                  |                                                | UVP threshold                | VIN_OV_FAULT_RESPONSE                             | int                                                                     | terval (hiccup). Note                        | 3.       | % V <sub>0</sub> |

|                                  |                                                |                              | PMBus configurable                                |                                                                         |                                              |          | · · ·            |

| Output vo                        | ultane                                         | UVP threshold range          | VOUT_UV_FAULT_LIMIT                               |                                                                         | 0-100                                        |          | % V <sub>0</sub> |

|                                  | er Voltage Protection,                         | OVP threshold                | DMD                                               |                                                                         | 115                                          |          | % V <sub>0</sub> |

| OVP/UVP                          |                                                | OVP threshold range          | PMBus configurable VOUT_OV_FAULT_LIMIT            |                                                                         | 100-115                                      |          | % V <sub>0</sub> |

|                                  |                                                | Fault response               | VOUT_UV_FAULT_RESPONSE<br>VOUT_OV_FAULT_RESPONSE  | Shutdown, make continuous restarts at 700 ms interval (hiccup). Note 3. |                                              |          |                  |

|                                  |                                                | OCP threshold                | Set value                                         |                                                                         | 10                                           |          | Α                |

| Over Curr                        | ent Protection,                                | OCP threshold range          | PMBus configurable IOUT_OC_FAULT_LIMIT            |                                                                         | 0-10                                         |          | Α                |

| UUP                              |                                                | Fault response               | IOUT_OC_FAULT_RESPONSE                            |                                                                         | ake continuous rest<br>terval (hiccup). Note |          |                  |

|                                  |                                                | OTP threshold                | Note 4                                            |                                                                         | 120                                          |          | °C               |

| Over Tem                         | perature Protection,                           | OTP threshold range          | PMBus configurable OT_FAULT_LIMIT                 |                                                                         | -40+120                                      | $\Box$   | °C               |

| OTP OTP                          |                                                | OTP hysteresis               | PMBus configurable                                |                                                                         | 15                                           |          | °C               |

|                                  |                                                | Fault response               | OT_FAULT_RESPONSE                                 |                                                                         | ake continuous rest<br>terval (hiccup). Note |          |                  |

| Oue: T-                          | noratura Chutal                                | Threshold                    | Note 4                                            |                                                                         | 150                                          | -        | °C               |

|                                  | perature Shutdown<br>e controlled)             | Hysteresis                   |                                                   |                                                                         | 20                                           |          | °C               |

| `                                |                                                | Accuracy                     |                                                   |                                                                         | ±20                                          |          | °C               |

| $V_{OL}$                         | Logic output low si                            | gnal level                   | SCL, SDA, SYNC, SALERT, PG                        |                                                                         |                                              | 0.4      | V                |

|                                  |                                                |                              |                                                   | 1                                                                       | 1                                            |          |                  |

6A Digital PoL DC-DC Converter Series

## **PRELIMINARY**

| Characteri              | stics                     |                                            | Conditions                                                     | Min     | Тур               | Max      | Unit             |

|-------------------------|---------------------------|--------------------------------------------|----------------------------------------------------------------|---------|-------------------|----------|------------------|

| I <sub>oL</sub>         | Logic output low si       | ink current                                |                                                                |         |                   | 4        | mA               |

| I <sub>OH</sub>         | Logic output high s       | source current                             |                                                                |         |                   | 4        | mA               |

| V <sub>II</sub>         | Logic input low thr       | eshold                                     | COL CDA OTDL CVAIC                                             |         |                   | 0.8      | V                |

| V <sub>IH</sub>         | Logic input high th       |                                            | SCL, SDA, CTRL, SYNC                                           | 2       |                   |          | V                |

| I <sub>IL CTRL</sub>    | Logic input low sin       |                                            | CTRL                                                           |         |                   | 0.5      | mA               |

| I <sub>I LEAK</sub>     | Logic leakage curr        |                                            | SCL, SDA, SYNC, SALERT, PG                                     |         |                   | 10       | uA               |

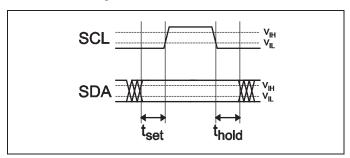

| f <sub>SMB</sub>        | SMBus Operating frequency |                                            |                                                                |         | 400               |          | kHz              |

|                         |                           |                                            | STOP bit to START bit                                          |         |                   |          |                  |

| T <sub>BUF</sub>        | SMBus Bus free tir        |                                            | See section SMBus – Timing                                     | 1.3     |                   |          | μs               |

| t <sub>set</sub>        | SMBus SDA setup           |                                            |                                                                | 100     |                   |          | ns               |

| t <sub>hold</sub>       | SMBus SDA hold ti         |                                            |                                                                | 300     |                   |          | ns               |

|                         |                           | P condition setup/hold time from SCL       |                                                                | 600     |                   |          | ns               |

| T <sub>low</sub>        | SCL low period            |                                            |                                                                | 1.3     |                   |          | μs               |

| T <sub>high</sub>       | SCL high period           |                                            |                                                                | 0.6     |                   |          | μs               |

| 1-141-1141              | #!                        |                                            | Frank W. M. da made to be availabled                           |         | 00                | 1        |                  |

| Initialization          | time                      | 18.1                                       | From V <sub>1</sub> > V <sub>UVLO</sub> to ready to be enabled |         | 23                |          | ms               |

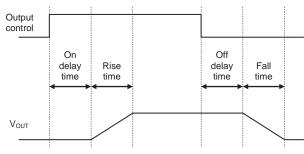

|                         |                           | Delay duration                             | DIAD (C. 11                                                    |         | 10                |          | ms               |

| Soft-start              |                           | Delay duration range                       | PMBus configurable<br>TON_DELAY                                |         | 1-145             |          | ms               |

| On Delay Tir            | ne                        | Delay set resolution                       |                                                                |         | 0.6               |          | ms               |

| Note 5                  |                           | Delay set accuracy                         | TON_DELAY value sent versus read-<br>back                      | ±0.5    | x Delay set resol | ution    | ms               |

|                         |                           | Delay accuracy                             | Actual delay duration versus TON_DE-<br>LAY read-back          |         | ±0.8              |          | ms               |

|                         |                           | Ramp duration                              | LAI Teau-back                                                  |         | 10                |          | ms               |

| Soft-start<br>Rise Time |                           | Ramp duration range                        | PMBus configurable TON_RISE                                    | 1 - (25 | 55 x Ramp set res | olution) | ms               |

| (0-100% of              | V )                       | Ramp set resolution                        | Varies with V <sub>o</sub>                                     | 0.4     |                   | 1        | ms               |

| (0-100 /6 01            | v <sub>0</sub> )          | Ramp set accuracy                          | TON_RISE value sent versus read-back                           |         | x Ramp set reso   |          |                  |

| Note F                  |                           | namp set accuracy                          |                                                                | ±0.0    | x namp secreso    | luuon    | ms               |

| Note 5                  |                           | Ramp time accuracy                         | Actual ramp duration versus TON_RISE read-back                 |         | ±10               |          | μs               |

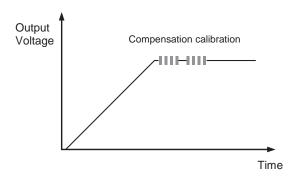

|                         |                           | Signal duration                            |                                                                |         | 5                 |          | ms               |

|                         | 0 111 11                  |                                            | $V_0 = 0.6 \text{ V}$                                          |         | 3.5               |          |                  |

| Compensati              | on Calibration            | Signal level                               | $V_0 = 1.2 - 3.3 \text{ V}$                                    |         | 2.5               |          | % V <sub>0</sub> |

|                         |                           |                                            | $V_0 = 5.0 \text{ V}$                                          |         | 2                 |          | 1                |

|                         |                           |                                            |                                                                |         |                   | 1        |                  |

|                         |                           |                                            | Rising                                                         |         | 90                |          | % V <sub>0</sub> |

|                         |                           | PG threshold                               | Falling                                                        |         | 85                |          | % V <sub>0</sub> |

|                         |                           |                                            | Tracking mode                                                  |         | 450               |          | mV               |

|                         |                           |                                            | See section Voltage Tracking                                   |         | 100               |          |                  |

|                         |                           | PG thresholds range<br>(Non-tracking only) | PMBus configurable POWER_GOOD_ON POWER_GOOD_OFF                | 0       |                   | 100      | % V <sub>0</sub> |

| Power Good              | , PG                      | PG delay                                   | From V <sub>0</sub> reaching target to PG assertion            |         | 11                |          | ms               |

|                         |                           | Enabled compensation calibration (default) | Tracking mode<br>See section Voltage Tracking                  |         | 20                |          | ms               |

|                         |                           | PG delay                                   | From $V_0$ reaching PG rising threshold to PG assertion        |         | 0                 |          | ms               |

|                         |                           | Disabled compensation calibration          | Tracking mode<br>See section Voltage Tracking                  |         | 20                |          | ms               |

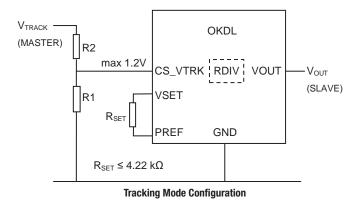

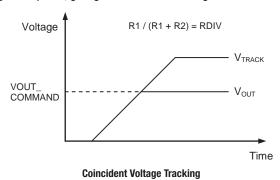

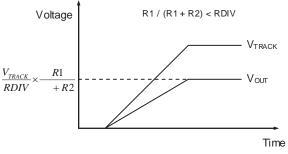

| Tracking Inp            | out Voltage Range         |                                            | CS_VTRK pin<br>Note 6                                          | 0       |                   | 1.2      | V                |

| Trooking Ass            | ouroov                    |                                            | 11010 0                                                        | -100    |                   | 100      | m\/              |

| Tracking Acc            | buidby                    |                                            |                                                                | -100    |                   | 100      | mV               |

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

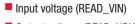

| Characteristics     |                                 | Conditions                                        | Min | Тур  | Max | Unit             |

|---------------------|---------------------------------|---------------------------------------------------|-----|------|-----|------------------|

|                     | Input voltage<br>READ_VIN       |                                                   |     | ±3   |     | % V <sub>1</sub> |

|                     | Output voltage<br>READ_VOUT     |                                                   |     | ±1   |     | % V <sub>o</sub> |

|                     | Output current<br>READ IOUT     | $TP_1 = 0-95^{\circ}C, V_1 = 4.5-14 V, I_0 > 5 A$ |     | ±8.5 |     | % I <sub>0</sub> |

| Monitoring accuracy | Note 7                          | $TP_1 = 0-95^{\circ}C, V_1 = 4.5-14 V, I_0 < 5 A$ |     | ±0.4 |     | A                |

|                     | Temperature READ_ TEMPERATURE_1 | Note 4                                            | -5  |      | 5   | °C               |

|                     | Duty cycle                      | Duty cycle < 10%                                  | -3  |      | 3   | %                |

|                     | READ_DUTY_CYCLE                 | Duty cycle > 10%                                  | -1  | ±0.5 | 1   | %                |

Note 1. Value refers to total (internal + external) effective output capacitance. Capacitance derating with VO typical for ceramic capacitors (bias characteristics) and temperature variations must be considered for the external capacitor(s). See section External Output Capacitors.

Note 2. A switching frequency close to 475 kHz should not be used since this frequency represents a boundary of two operational modes of the product. There are configuration changes to consider when changing the switching frequency, see section Switching Frequency.

Note 3.The restart interval is configurable between 100ms and 700ms in 100ms steps. Severe overcurrent faults occurring with VO > 2.5V may result in a restart interval of 1200 ms instead of the configured value. See operating conditions for other fault response alternatives.

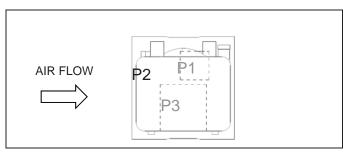

Note 4. Temperature measured internally at temperature position P3. See section Over Temperature Protection. Note 5. Same specification applies for soft-stop and TOFF\_DELAY/TOFF\_FALL if enabled. The internal ramp and delay generators can only achieve certain discrete timing values. A written TON/OFF\_DELAY or TON/OFF\_RISE value will be rounded to the closest achievable value, thus a command read-back provides the actual set value. See section Soft-Start and Soft-Stop.

Note 6.Larger tracking input range is provided by external resistor divider, see section Voltage Tracking. Note 7. At VO > 3.5V and VO / VI in the approximate range 55-70% there may be an additional current monitoring inaccuracy on the negative side up to -1 A.

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

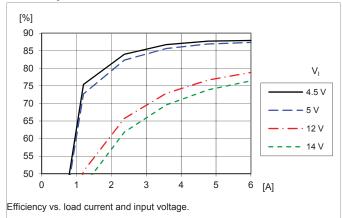

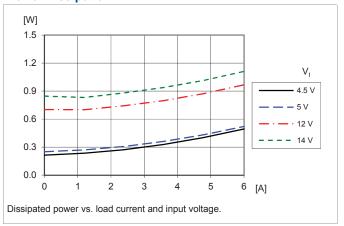

# Typical Characteristics, $V_0 = 0.6 \text{ V}$ Default Configuration, $T_{P1} = +25 ^{\circ}\text{C}$

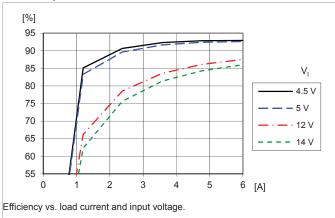

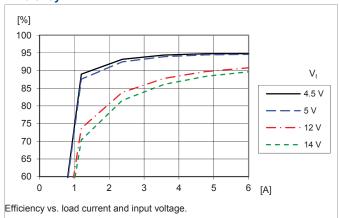

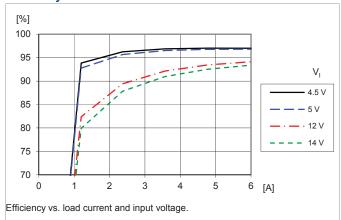

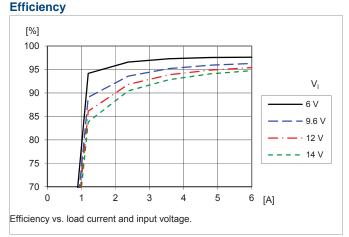

#### **Efficiency**

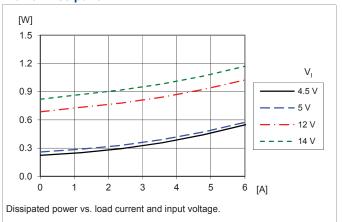

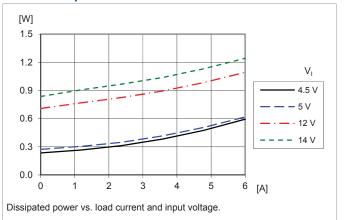

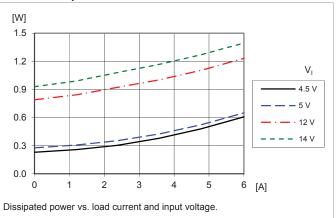

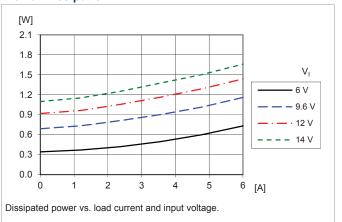

#### **Power Dissipation**

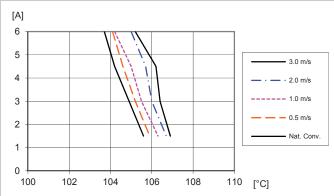

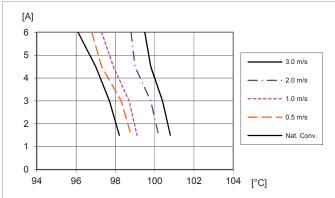

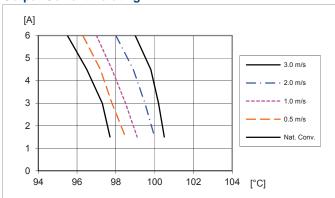

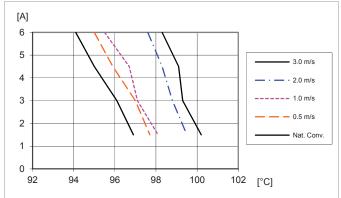

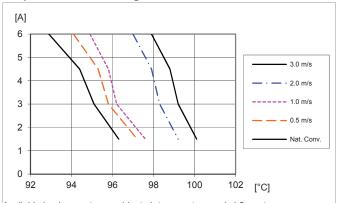

#### **Output Current Derating**

Available load current vs. ambient air temperature and airflow at V<sub>I</sub> = 12 V. See section Thermal Consideration.

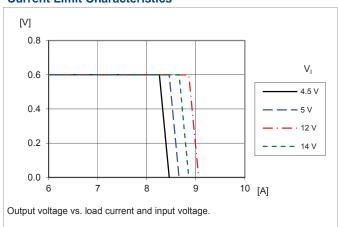

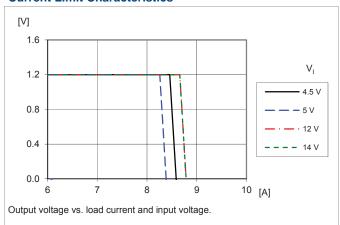

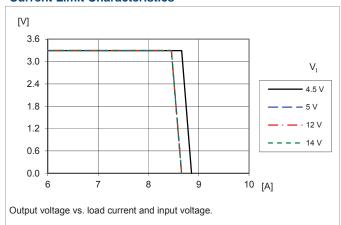

#### **Current Limit Characteristics**

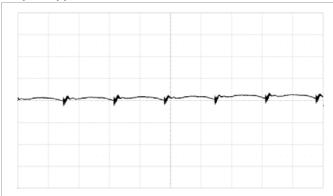

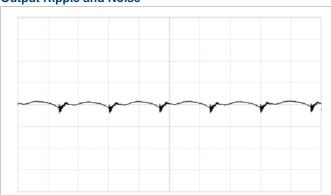

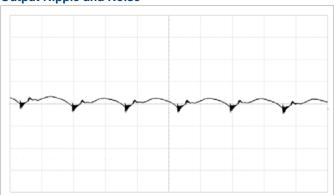

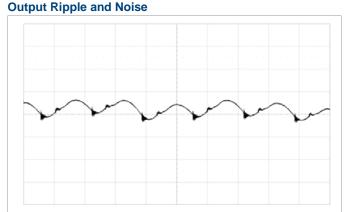

#### **Output Ripple and Noise**

Fundamental output voltage ripple at  $V_1$ = 12 V,  $C_0$ = 3x100  $\mu$ F,  $I_0$ = 6 A. Scale: 5 mV/div, 1  $\mu$ s/div, 20 MHz bandwidth. See section Output Ripple and Noise.

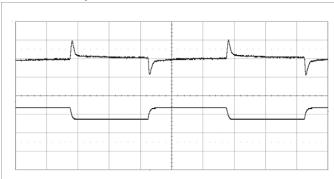

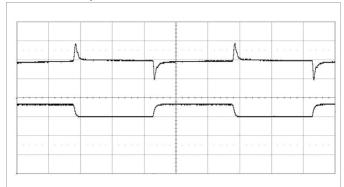

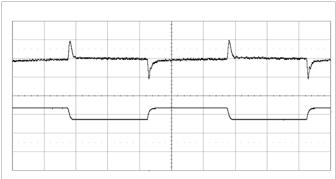

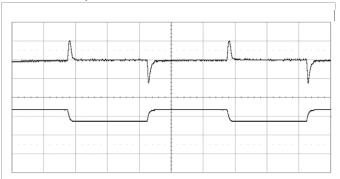

#### **Transient Response**

Output voltage response to load current step change (1.5–4.5–1.5 A) at V<sub>I</sub>= 12 V, C<sub>O</sub>=  $3x100~\mu\text{F}+270~\mu\text{F}/10\text{m}\Omega$ . Default compensation settings. Scale: 20~mV/div, 5~A/div,  $100~\mu\text{s/div}$ .

### **PRELIMINARY**

# Typical Characteristics, $V_0 = 1.2 \text{ V}$ Default Configuration, $T_{P1} = +25 ^{\circ}\text{C}$

#### **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

Available load current vs. ambient air temperature and airflow at V<sub>I</sub> = 12 V. See section Thermal Consideration.

#### **Current Limit Characteristics**

#### **Output Ripple and Noise**

Fundamental output voltage ripple at  $V_l$  = 12 V,  $C_O$  = 3x100  $\mu$ F,  $I_O$  = 6A. Scale: 5 mV/div, 1  $\mu$ s/div, 20 MHz bandwidth. See section Output Ripple and Noise.

#### **Transient Response**

Output voltage response to load current step change (1.5–4.5–1.5 A) at V<sub>I</sub>= 12 V, C<sub>O</sub>=  $3x100~\mu\text{F}+270~\mu\text{F}/10\text{m}\Omega$ . Default compensation settings. Scale: 20 mV/div, 5 A/div, 100  $\mu\text{s}/\text{div}$ .

### **PRELIMINARY**

# Typical Characteristics, $V_0$ = 1.8 V Default Configuration, $T_{P1}$ = +25°C

#### **Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

Available load current vs. ambient air temperature and airflow at V<sub>I</sub> = 12 V. See section Thermal Consideration.

#### **Current Limit Characteristics**

#### **Output Ripple and Noise**

Fundamental output voltage ripple at  $V_1 = 12 \text{ V}$ ,  $C_0 = 3x100 \mu\text{F}$ ,  $I_0 = 6 \text{ A}$ . Scale: 5 mV/div, 1 µs/div, 20 MHz bandwidth. See section Output Ripple and Noise.

#### **Transient Response**

Output voltage response to load current step change (1.5-4.5-1.5 A) at  $V_l$  = 12 V,  $C_0$  = 3x100  $\mu F$  + 270  $\mu F/10m\Omega$ . Default compensation settings. Scale: 20 mV/div, 5 A/div, 100  $\mu s/div$ .

### **PRELIMINARY**

# Typical Characteristics, $V_0 = 3.3 \text{ V}$ Default Configuration, $T_{P1} = +25^{\circ}\text{C}$

**Efficiency**

#### **Power Dissipation**

#### **Output Current Derating**

Available load current vs. ambient air temperature and airflow at  $V_1$  = 12 V. See section Thermal Consideration.

#### **Current Limit Characteristics**

Fundamental output voltage ripple at V<sub>I</sub> = 12 V, C<sub>O</sub> = 3x100  $\mu$ F, I<sub>O</sub> = 6 A. Scale: 5 mV/div, 1  $\mu$ s/div, 20 MHz bandwidth. See section Output Ripple and Noise.

#### **Transient Response**

Output voltage response to load current step change (1.5–4.5–1.5 A) at V<sub>I</sub>= 12 V, C<sub>O</sub>=  $3x100~\mu\text{F}+270~\mu\text{F}/10\text{m}\Omega$ . Default compensation settings. Scale: 20~mV/div, 5~A/div,  $100~\mu\text{s/div}$ .

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

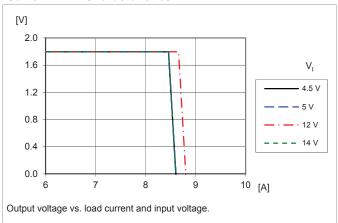

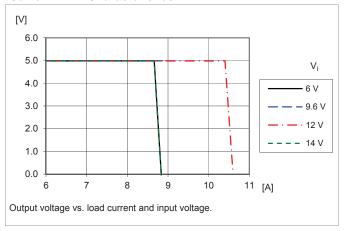

# Typical Characteristics, $V_0 = 5.0 \text{ V}$ Default Configuration, $T_{P1} = +25^{\circ}\text{C}$

#### **Power Dissipation**

#### **Output Current Derating**

Available load current vs. ambient air temperature and airflow at V<sub>I</sub> = 12 V. See section Thermal Consideration.

#### **Current Limit Characteristics**

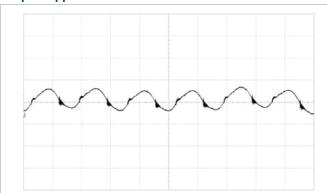

#### **Output Ripple and Noise**

Fundamental output voltage ripple at  $V_1$  = 12 V,  $C_0$  = 3x100  $\mu$ F,  $I_0$  = 6A. Scale: 5 mV/div, 1 µs/div, 20 MHz bandwidth. See section Output Ripple and Noise.

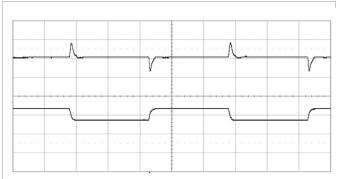

#### **Transient Response**

Output voltage response to load current step change (1.5-4.5-1.5 A) at  $V_1$ = 12 V,  $C_0$  = 3x100 μF + 270 μF/10m $\Omega$ . Default compensation settings. Scale: 50 mV/div, 5 A/div, 100 µs/div.

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

#### **Typical Characteristics**

Default Configuration,  $T_{P1} = +25$ °C,  $V_O = 3.3 \text{ V}$

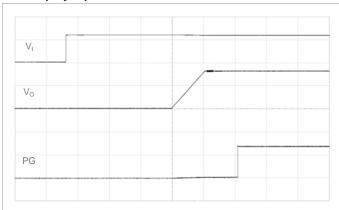

#### Start-up by input source

Start-up enabled by applying V<sub>I</sub>. TON\_DELAY = TON\_RISE = 10 ms (default). V<sub>I</sub> = 12 V, I<sub>O</sub> = max I<sub>O</sub>, PG pulled up to V<sub>O</sub>. Scale: 10 or 2 V/div, 10 ms/div.

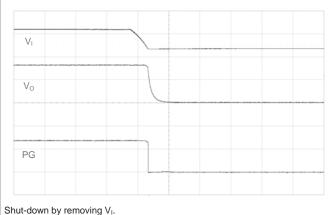

#### Shut-down by input source

Shut-down by removing  $V_{\rm l}.$   $V_{\rm l}$  = 12 V,  $I_{\rm O}$  = max  $I_{\rm O}$ , PG pulled up to  $V_{\rm O}.$  Scale: 10 or 2 V/div, 1 ms/div.

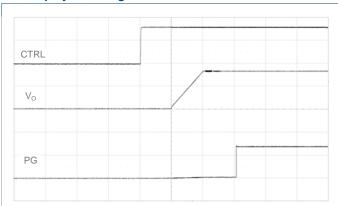

#### Start-up by CTRL signal

Start-up enabled by CTRL signal. TON\_DELAY = TON\_RISE = 10 ms (default).  $V_1 = 12 \text{ V}$ ,  $I_0 = \text{max } I_0$ , PG pulled up to  $V_0$ .

Scale: 2 V/div, 10 ms/div.

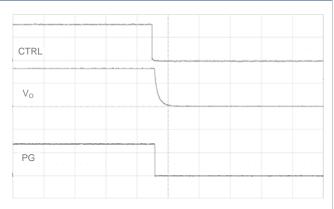

#### Shutdown by CTRL signal

Shut-down by CTRL signal.  $V_1 = 12 \text{ V}$ ,  $I_0 = \text{max } I_0$ , PG pulled up to  $V_0$ . Scale: 2 V/div, 1 ms/div.

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

#### **EMC Specification**

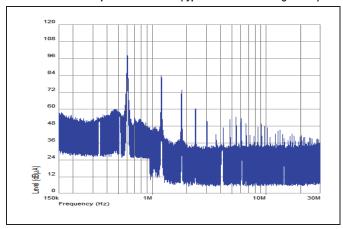

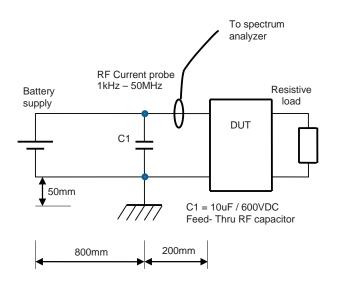

Conducted EMI is measured according to the test set-up below. The fundamental switching frequency is 600 kHz.

#### Conducted EMI Input terminal value (typical for default configuration)

**EMI** without filter

Test set-up conducted emission, power lead

#### **Layout Recommendations**

The radiated EMI performance of the product will depend on the PWB layout and ground layer design. It is also important to consider the standoff of the product. If a ground layer is used, it should be connected to the output of the product and the equipment ground or chassis.

A ground layer will increase the stray capacitance in the PWB and improve the high frequency EMC performance.

#### **Output Ripple and Noise**

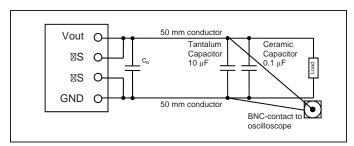

Output ripple and noise is measured according to figure below.

A 50 mm conductor works as a small inductor forming together with the two capacitances a damped filter.

Output ripple and noise test set-up

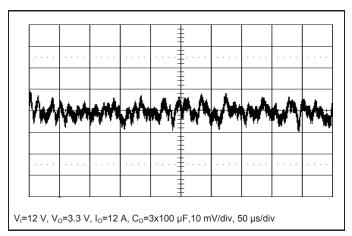

The digital compensation of the product is designed to automatically provide stability, accurate line and load regulation and good transient performance for a wide range of operating conditions (switching frequency, input voltage, output voltage, output capacitance). Inherent from the implementation and normal to the product there will be some low-frequency noise or wander at the output, in addition to the fundamental switching frequency output ripple. The total output ripple and noise is maintained at a low level.

Example of low frequency noise at the output

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

#### Operating information

#### **Power Management Overview**

This product is equipped with a PMBus interface. The product incorporates a wide range of readable and configurable power management features that are simple to implement

with a minimum of external components. Additionally, the product includes protection features that continuously safeguard the load from damage due to unexpected system faults. A fault is also shown as an alert on the SALERT pin.

The product is delivered with a default configuration suitable for a wide range of operation in terms of input voltage, output voltage, and load. The configuration is stored in an internal Non-Volatile Memory (NVM). All power management functions can be reconfigured using the PMBus interface. Please contact your local Murata Power Solutions representative for design support of custom configurations or appropriate SW tools for design and download of your own configurations.

#### **Input Under Voltage Lockout, UVLO**

The product provides a non-configurable under voltage lockout (UVLO) circuit that monitors the internal supply of the converter. Below a certain input voltage level the internal supply will be too low for proper operation and the product will be in under voltage lockout, not switching or responding to the CTRL pin or to PMBus commands.

#### **Input Over Voltage Lockout, OVLO**

The product provides a non-configurable over voltage lockout (OVLO) circuit that will shut down the product when the input voltage rises above a certain level. The product will not switch, respond to the CTRL pin or to PMBus commands when being in over voltage lockout.

#### **Input Turn-On and Turn-Off Voltage**

The product monitors the input voltage and will turn-on and turn-off the output at configured levels (assuming the product is enabled by CTRL pin or PMBus). The default turn-on input voltage level is 4.35 V whereas the corresponding turn-off input voltage level is 3.8 V. The turn-on and turn-off levels may be reconfigured using the PMBus commands VIN\_ON and VIN\_OFF.

### **Input Under Voltage Protection (IUVP)**

The product monitors the input voltage continously and will respond as configured when the input voltage falls below the configured threshold level. The product can respond in a number of ways as follows:

- 1. Continue operating without interruption.

- 2. Continue operating for a given delay period, followed by an output voltage shutdown if the fault still exists.

- 3. Immediate and definite shutdown of output voltage until the fault is cleared by PMBus or the output voltage is re-enabled.

- 4. Immediate shutdown of output voltage while the fault is present. Operation resumes and the output is enabled when the fault condition no longer exists.

The default response is 4. The IUVP function can be reconfidured using the PMBus commands VIN UV FAULT LIMIT and VIN UV FAULT RESPONSE.

#### **Input Over Voltage Protection (IOVP)**

The product monitors the input voltage continously and will respond as configured when the input voltage rises above the configured threshold level. Refer to section "Input Under Voltage Protection" for response configuration options and default setting.

#### **Input and Output Impedance**

The impedance of both the input source and the load will interact with the impedance of the product. It is important that the input source has low characteristic impedance. If the input voltage source contains significant inductance, the addition of a capacitor with low ESR at the input of the product will ensure stable operation.

#### **External Input Capacitors**

The input ripple RMS current in a buck converter can be estimated to Eq. 1.  $I_{inputRMS} = I_{load} \sqrt{D(1-D)}$ ,

where  $I_{load}$  is the output load current and D is the duty cycle. The maxi mum load ripple current becomes  $I_{load}/2$ . The ripple current is divided into three parts, i.e., currents in the input source, external input capacitor, and internal input capacitor. How the current is divided depends on the impedance of the input source, ESR and capacitance values in the capacitors.

For most applications non-tantalum capacitors are preferred due to the robustness of such capacitors to accommodate high inrush currents of systems being powered from very low impedance sources. It is recommended to use a combination of ceramic capacitors and low-ESR electrolytic/polymer bulk capacitors. The low ESR of ceramic capacitors effectively limits the input ripple voltage level, while the bulk capacitance minimizes deviations in the input voltage at large load transients.

It is recommended to use at least 47 uF of ceramic input capacitance. At duty cycles between 25% and 75% where the input ripple current increases (see Eq. 1), additional ceramic capacitance will help to keep the input ripple voltage low. The required bulk capacitance depends on the impedance of the input source and the load transient levels at the output. In general a low-ESR bulk capacitor of at least 100 uF is recommended. The larger the duty cycle is, the larger impact an output load step will have on the input side, thus the larger bulk capacitance is required to limit the input voltage deviation.

If several products are connected in a phase spreading setup the amount of input capacitance per product can be reduced.

Input Capacitors must be placed closely and with low impedance connections to the VIN and GND pins in order to be effective.

#### **External Output Capacitors**

The output capacitor requirement depends on two considerations; output ripple voltage and load transient response. To achieve low

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

ripple voltage, the output capacitor bank must have a low ESR value, which is achieved with ceramic output capacitors. A small output voltage deviation during load transients is achieved by using a larger amount of capacitance. Designs with smaller load transients can use fewer capacitors and designs with more dynamic load content will require more load capacitors to achieve a small output deviation. Improved transient response can also be achieved by adjusting the settings of the control loop of the product (see section Compensation Implementation).

It is recommended to locate low ESR ceramic and low ESR electrolytic/polymer capacitors as close to the load as possible, using several capacitors in parallel to lower the effective ESR. It is important to use low resistance and low inductance PCB layouts and cabling in order for capacitance to be effective.

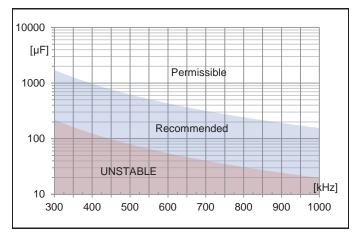

The control loop of the product is optimized to operate with low-ESR output capacitors and is capable of achieving a fast loop transient response with a reduced amount of capacitance. The effective output capacitance is recommended to be in the range [COUT low, COUT high] according to equations Eq. 2 and Eq. 3 below, where FSW is the switching frequency. The compensation implementation of the product is optimized for this range.

Eq. 2.

$$C_{OUT\_low} = \frac{2.6 \cdot 10^7}{(F_{SW})^2}$$

Eq. 3.

$$C_{OUT\_high} = \frac{16 \cdot 10^7}{(F_{SW})^2}$$

Effective total output capacitance limits vs switching frequency.

The product permits a large range of output capacitance, thus capacitance above COUT high is acceptable. This capability is important in applications where the output capacitance may be unknown or not well controlled or in applications where a large amount of output

capacitance is required. The limit of COUT\_low must be followed in order to guarantee stability.

Note that Eq. 2 and Eq. 3 and the chart above refer to the total capacitance at the output, thus including both the capacitance internal to the product and the external capacitance applied in the application. The internal output capacitance is listed in the Electrical Characteristics table.

Note also that Eq. 2 and Eq. 3 and the chart refers to the effective capacitance, not taking into account the capacitance derating that applies for ceramic capacitors with increased voltage or temperature variations.

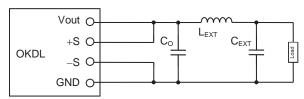

In cases where the external output filter includes an inductor (forming a pi filter) according to the picture below, the following must be considered.

External output filter with inductor (pi filter).

In order for the compensation calibration (see next sections) to give a reliable result, the following condition should be fulfilled:

$$F_{LC_{-EXT}} = \frac{1}{2\pi\sqrt{L_{EXT}\,C_{EXT}}} > \frac{F_{SW}}{10}$$

where FLC\_EXT is the resonance frequency of the external filter and FSW is the switching frequency. If there are multiple pi filters in parallel on the output, giving a more complex transfer function with several resonance peaks, each of the peaks should be above FSW/10.

If this condition is not fulfilled it is recommended to disable compensation calibration and set FLC manually in COMP MODEL (see next sections). Please contact your Murata Power Solutions sales representative for further support.

For the OKDL products, it is recommended that the remote sense connections are made at a point before the external inductor, as illustrated in the drawing above.

#### **Dynamic Loop Compensation (DLC)**

The typical design of regulated power converters includes a control function with a feedback loop that can be closed using either analog or digital circuits. The feedback loop is required to provide a stable output voltage, but should be optimized for the output filter to maintain output voltage regulation during transient conditions such as sudden changes in output current and/or input voltage. Digitally controlled converters allow one to optimize loop parameters without the need to change components on the board, however, optimization

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

can still be challenging because the key parameters of the output filter include parasitic impedances in the PCB and the often distributed filter components themselves.

Dynamic Loop Compensation has been developed to solve the problem of compensation for a converter with a difficult to define output filter. This task is achieved by utilization of algorithms that can characterize an arbitrary output filter based on behavior of the output voltage in response to a disturbance initiated by the algorithm, or occurring due to the changes in operating conditions, and automatically adjust feedback loop parameters to match the output filter.

Details of the algorithm that is used to characterize an output filter and the different operational modes can be found in the following sections.

#### **Compensation Implementation**

Unlike PID-based digital power regulators the product uses a statespace model based algorithm that is valid for both the small- and large-signal response and accounts for duty-cycle saturation effects. This eliminates the need for users to determine and set thresholds for transitioning from linear to nonlinear modes. These capabilities result in fast loop transient response and the possibility of reducing the number of output capacitors.

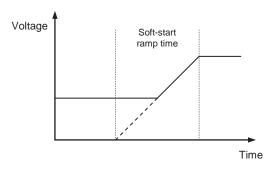

Compensation calibration is when the resonance frequency FLC of the output stage is measured. The FLC value is used to automatically control the compensation. During ramp-up of the output voltage, robust and low bandwidth default compensation settings are used based on the default FLC value assigned by bits 15:0 in PMBus command COMP MODEL. If the switching frequency is changed the default FLC should be adjusted according to Eq. 4 to maintain robust settings.

Eq. 4.

$$F_{LC\_DEFAULT} = \frac{F_{SW}}{32}$$

It is possible for the user to write any FLC value in COMP MODEL to be used during ramp-up. This is useful in cases where improved dynamic performance is needed during ramp-up. User assignment of FLC in COMP MODEL is also needed when calibration is disabled, since in such case the FLC value used during ramp-up will continue to be used when ramp-up has finished.

When calibration is enabled (default), an AC low amplitude measurement signal is applied on the output immediately after ramp-up has finished. See Electrical Characteristics table for a specification of this measurement signal. During calibration the resonant frequency FLC of the power stage is measured. From the result an internal nonlinear model is constructed to optimize the bandwidth and transient response of the product. Pole locations of the closed system are automatically selected based on switching frequency, measured FLC and the output voltage level.

After each performed calibration, bits 15:0 in COMP\_MODEL are updated with measured FLC, thus this value can be read out by the user. Note however, as soon as the output voltage is disabled, the FLC value in COMP MODEL will revert back to the corresponding value stored in User NVM. Therefore, user values of COMP MODEL should be written to NVM, or, if written to RAM only, be written before each time the output voltage is enabled. COMP MODEL should only be changed in RAM while the output voltage is disabled.

By setting bit 2 in ADAPTIVE MODE a STORE USER ALL command will automatically be performed after the next calibration, effectively storing the measured FLC value in COMP MODEL 15:0 in NVM as the FLC value for subsequent ramp-ups.

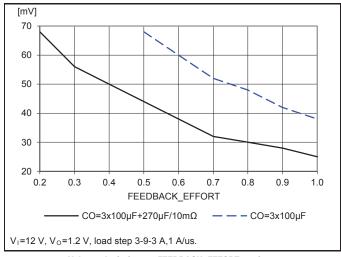

The table below shows an example of improvement in transient response due to the compensation calibration, compared to using the FLC DEFAULT value.

|                   | Non-calibrated compensation | Calibrated compensation |

|-------------------|-----------------------------|-------------------------|

| Voltage deviation | 53 mV                       | 34 mV                   |

| Recovery time     | 50 μs                       | 30 µs                   |

Load transient performance non-calibrated compensation with FLC DEFAULT vs. calibrated compensation.

VI=12 V, V0=1.2 V, C0 =  $3x100 \mu F + 270\mu F/10m\Omega$ , load step 3-9-3 A, 1 A/us.

The PMBus command ADAPTIVE MODE provides the user different options for compensation calibration:

- 1. Calibration is performed once after each ramp-up (default). (ADAP-TIVE MODE = 0x024B).

- 2. Calibration is performed once after first ramp-up after input voltage is applied (ADAPTIVE MODE = 0x124B).

- 3. Calibration is performed continuously after ramp-up at ~800 ms interval (ADAPTIVE MODE = 0x034B).

- 4. Calibration is disabled (ADAPTIVE\_MODE = 0x004B). The FLC value stored in bits 15:0 in COMP MODEL will be applied.

- 5. Calibration is performed continuously in response to a PMBus command. Controlled by setting/clearing bit 8 in ADAPTIVE MODE during operation.

Compensation may be set more or less aggressive by adjusting the feedback gain factor, controlled by the PMBus command FEED-BACK\_EFFORT. This parameter is proportional to the open loop gain of the system. Increasing the gain, i.e the control effort, will reduce the voltage deviation at load transients, at the expense of somewhat increased jitter and noise on the output. Users also have access to

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

the PMBus command ZETAP, which corresponds to the damping ratio of the closed loop system. By default the product uses 0.5 as the feedback gain factor and 1.5 for damping ratio, to target a system bandwidth of 10% of the switching frequency.

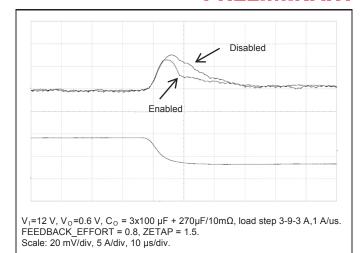

In some operating conditions at low output voltages, it is possible to enhance the recovery time at load release by enabling Negative Duty Cycle by PMBus command LOOP CONFIG.

The graphs below exemplify the impact on load transient performance when adjusting the feedback gain factor, the damping ratio and the Negative Duty Cycle feature.

Voltage deviation vs. FEEDBACK EFFORT setting.

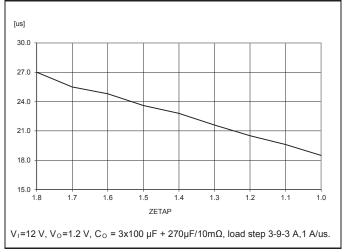

Recovery time to within 1% of VO vs. ZETAP setting.

Load release response at enabled/disabled Negative Duty Cycle at low output voltage.

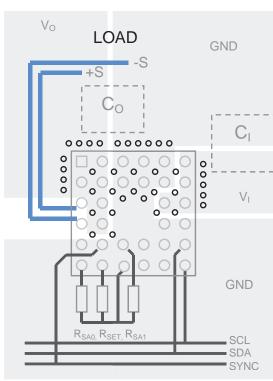

#### **Remote Sense**

The product has remote sense that can be used to compensate for voltage drops between the output and the point of load. The sense traces should be located close to the PWB ground layer to reduce noise susceptibility. Due to derating of internal output capacitance the voltage drop should be kept below VDROPMAX = (5.25 - VOUT) / 2. A large voltage drop will impact the electrical performance of the regulator. If the remote sense is not needed +S must be connected to VOUT and -S must be connected to GND.

#### **Output Voltage Control**

To control the output voltage the product features both a remote control input through the CTRL pin and a PMBus enable function by the command OPERATION. It is also possible to configure the output to be always on.

By default the output is controlled by the CTRL pin only. The output voltage control can be reconfigured using the PMBus command ON OFF CONFIG.

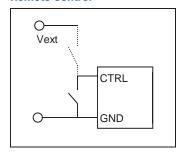

#### **Remote Control**

The product is equipped with a remote control function, i.e., the CTRL pin. The remote control can be connected to either the primary negative input connection (GND) or an external voltage (Vext). See Absolute Maximum Rating for maximum voltage level allowed at the CTRL pin.

The CTRL function allows the product to be turned on/off by an external device like a semiconductor or mechanical switch.

The CTRL pin has an internal 6.8 k $\Omega$  pull-up resistor to 3.3 V. The external device must provide a minimum required sink current to guarantee a voltage not higher than the logic low threshold level (see

6A Digital PoL DC-DC Converter Series

### **PRELIMINARY**

Electrical Characteristics). When the CTRL pin is left open, the voltage generated on the CTRL pin is 3.3 V.

By default the product provides "positive logic" RC and will turn on when the CTRL pin is left open and turn off when the CTRL pin is applied to GND. It is possible to configure "negative logic" instead by using the PMBus command ON OFF CONFIG.

If the device is to be synchronized to an external clock source, the clock frequency must be stable prior to asserting the CTRL pin.

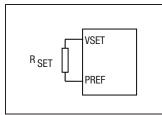

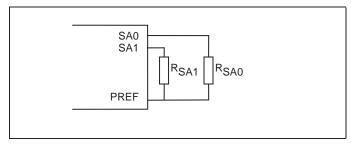

### **Output Voltage Adjust using Pin-strap Resistor**

Using an external Pin-strap resistor, RSET, the output voltage can be set in the range 0.6 V to 5.0 V at 16 different levels shown in the table below. The resistor should be applied between the VSET pin and the PREF pin.

RSET also sets the maximum output voltage; see section "Output Voltage Range Limitation". The resistor is sensed only at the application of input voltage. Changing the resistor value during normal operation will not change the output voltage. The input voltage must be at least 1 V larger than the output voltage in order to deliver the correct output voltage. See Ordering Information for output voltage range.

The following table shows recommended resistor values for RSET. Maximum 1% tolerance resistors are required.

| <b>V</b> <sub>OUT</sub> [V] | $R_{SET}[k\Omega]$ | <b>V</b> <sub>OUT</sub> [ <b>V</b> ] | $R_{SET}[k\Omega]$ |

|-----------------------------|--------------------|--------------------------------------|--------------------|

| 0.60                        | 5.11               | 1.05                                 | 17.8               |

| 0.70                        | 6.19               | 1.10                                 | 21.5               |

| 0.75                        | 7.15               | 1.20                                 | 26.1               |

| 0.80                        | 8.25               | 1.50                                 | 31.6               |

| 0.85                        | 9.53               | 1.80                                 | 38.3               |

| 0.90                        | 11.0               | 2.50                                 | 44.2               |

| 0.95                        | 12.7               | 3.30                                 | 51.1               |

| 1.00                        | 14.7               | 5.00                                 | 59.0               |

#### **Output Voltage Adjust using PMBus**

The output voltage set by pin-strap can be overridden using the PMBus command VOUT COMMAND. See Electrical Specification for adjustment range.

#### **Voltage Margining Up/Down**

Using the PMBus interface it is possible to adjust the output higher or lower than its nominal voltage setting in order to determine whether the load device is capable of operating over its specified supply voltage range. This provides a convenient method for dynamically testing the operation of the load circuit over its supply margin or range. It can also be used to verify the function of supply voltage supervisors. Margin limits of the nominal output voltage  $\pm 5\%$  are default, but

the margin limits can be reconfigured using the PMBus commands VOUT MARGIN LOW, VOUT MARGIN HIGH. Margining is activated by the command OPERATION.

#### **Output Voltage Trim**

The actual output voltage can be trimmed to optimize performance of a specific load by setting a non-zero value for PMBus command VOUT\_TRIM. The value of VOUT\_TRIM is summed with VOUT\_COM-MAND, allowing for multiple products to be commanded to a common nominal value, but with slight adjustments per load.

#### **Output Voltage Range Limitation**

The output voltage is by default limited to the least of 5.5 V or 110% of the nominal output voltage, where the nominal output voltage is defined by pin-strap or by VOUT COMMAND in Non-Volatile Memory (see section Initialization Procedure). This protects the load from an over voltage due to an accidentally written wrong VOUT COMMAND. The limitation applies to the regulated output voltage, rather than the internal value of VOUT COMMAND. The output voltage limit can be reconfigured using the PMBus command VOUT MAX.

Output Over Voltage Protection (OVP)